servlet

人工智能

vsprintf

microsoft

职场

ROS

概率论

two sum

记事本

OData

系统架构

Semaphore

网站安全防护

桌面聊天系统

程序员35

gnu

电路分析

k8s

从零到壹搭建一个商城架构

Firebase

directMemorty

Spark sql

岛屿问题

嵌入式闪存

设备管理系统

TEC

亚太数学建模竞赛

文本样式

冰蝎

PMO大会

窗口函数

opengl入门

车辆检测

Bean生命周期回调

eassyexcel

init.rc脚本

GPIO

并联机器人

flink 流批一体化

运营

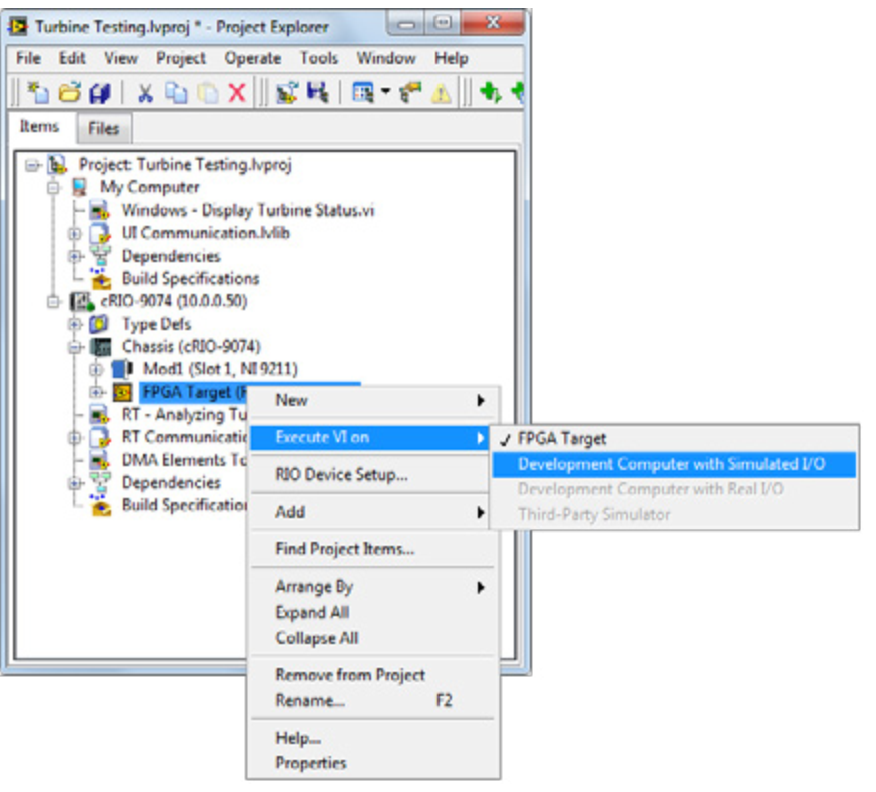

LabVIEWCompactRIO 开发指南33 测试和调试LabVIEW FPGA代码

LabVIEWCompactRIO 开发指南33

测试和调试LabVIEW FPGA代码

如前所述,应在仿真模式下开发LabVIEWFPGA VI,以快速迭代设计并避免冗长的编译时间。当需要测试和调试VI时,可以保持仿真模式或利用其他几个选项。应该根据功能验证与性能的要求以…

[静态时序分析简明教程(十)]组合电路路径set_max/min_delay

静态时序分析简明教程-组合电路路径 一、写在前面1.1 快速导航链接 二、组合电路路径2.1 SDC约束2.2 举例 三、总结 一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人…

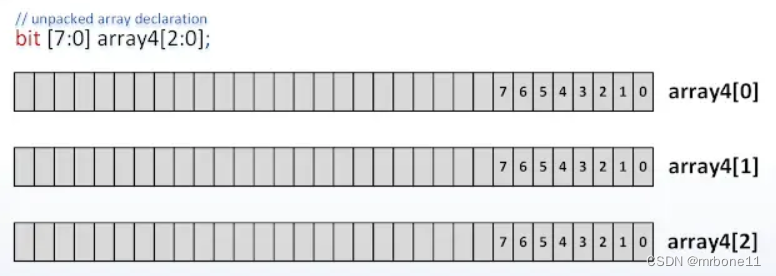

System Verilog-packed array以及unpacked array

如下声明:

logic [7:0] data [255:0]维度在标识符前面的部分称为packed array,在标识符后面的部分称为unpacked array,一维的pakced array也称为vector。

packed array

packed array只能由单bit数据类型(bit,logic,reg…

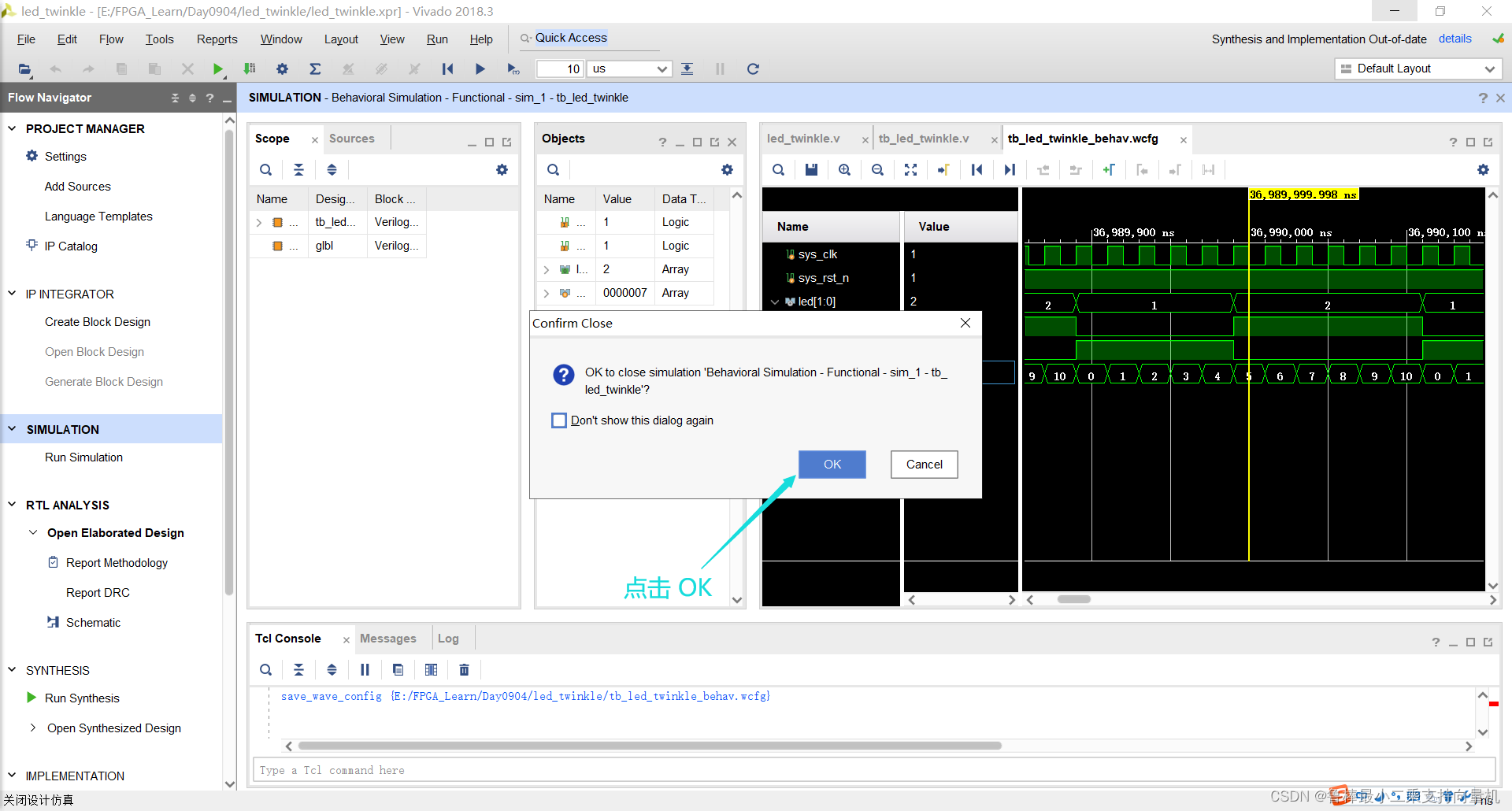

ZYNQ之FPGA学习----Vivado功能仿真

1 Vivado功能仿真

阅读本文需先学习: FPGA学习----Vivado软件使用

典型的FPGA设计流程,如图所示: 图片来自《领航者ZYNQ之FPGA开发指南》

Vivado 设计套件内部集成了仿真器 Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和…

FPGA实践 ——Verilog基本实验步骤演示

0x00 回顾:AND/OR/NOT 逻辑的特性

AND:与门可以具有两个或更多的输入,并返回一个输出。当所有输入值都为 1 时,输出值为 1。如果输入值中有任何一个为 0,则输出值为 0。

OR:或门可以具有两个或更多的输入…

[FPGA IP系列] FPGA常用存储资源大全(RAM、ROM、CAM、SRAM、DRAM、FLASH)

本文主要介绍FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等资源。

一、RAM

RAM(Random Access Memory)是FPGA中最基本和常用的内部存储块,根据不同架构可以实现不同容量,最大可达几十Mb。

FPGA中的RAM主要包括: 分布式RAM:存在于逻辑块…

[FPGA IP系列] 2分钟了解FPGA中的BRAM

FPGA设计中,BRAM是一项非常关键的内置存储资源,FPGA开发需要熟练使用BRAM,今天再复习一下BRAM的知识,包括BRAM的定义、组成、应用等等。

一、BRAM介绍

1、BRAM的定义

RAM是Random Access Memory,也就是随机访问数据…

[HDLBits] Exams/2012 q1g

Consider the function f shown in the Karnaugh map below. Implement this function.

(The original exam question asked for simplified SOP and POS forms of the function.) //

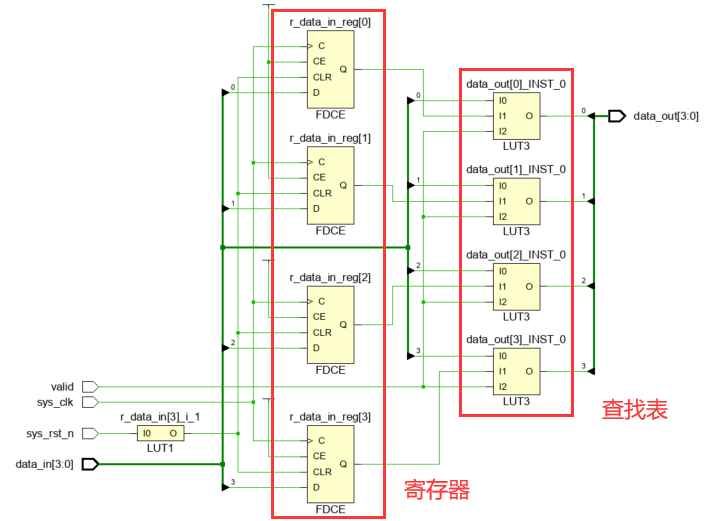

FPGA设计中锁存器产生、避免与消除

FPGA设计中锁存器产生、避免与消除 一、锁存器的产生1.1 组合逻辑中使用保持状态1.2 组合逻辑中的if-else语句或case语句未列出所有可能性1.3 小结 二、锁存器的避免三、锁存器的消除3.1 情况一 一、锁存器的产生 锁存器的产生主要有以下两种情况:(1&…

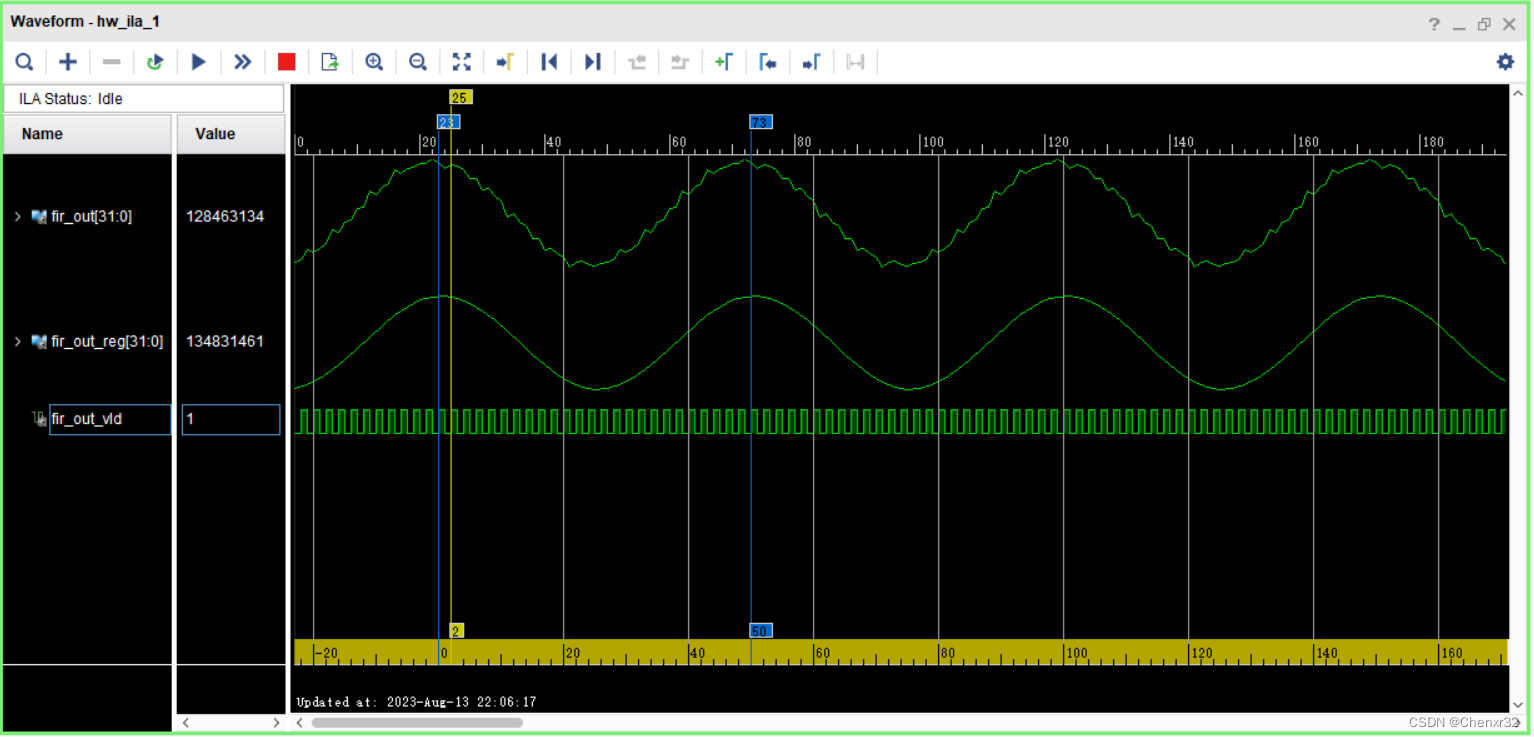

HLS+System Generator实现FIR低通滤波器

硬件:ZYNQ7010 软件:MATLAB 2019b、Vivado 2017.4、HLS 2017.4、System Generator 2017.4

1、MATLAB设计低通滤波器 FPGA系统时钟 50MHz,也是采样频率。用 MATLAB 生成 1MHz 和 10MHz 的正弦波叠加的信号,并量化为 14bit 整数。把…

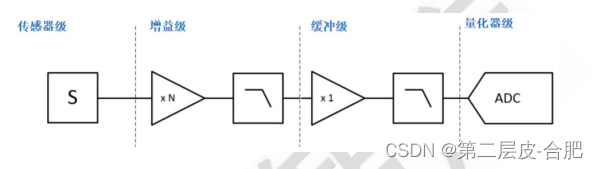

16通道AD采集FMC子卡推荐哪些?

FMC149是一款16通道65MHz采样率14位直流耦合AD采集FMC子卡,符合VITA57.1规范,可以作为一个理想的IO模块耦合至FPGA前端,16通道AD通过FMC连接器(HPC)连接至FPGA从而大大降低了系统信号延迟。

该板卡支持板上可编程采样…

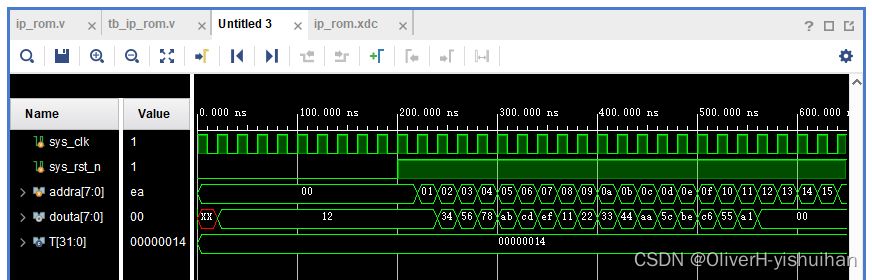

Vivado 下 IP核 之ROM 读写

目录

Vivado 下 IP核 之ROM 读写

1、实验简介

2、ROM IP 核简介

3、ROM IP 核配置

3.1、创建 ROM 初始化文件

3.2、单端口 ROM 的配置

3.3、双端口 ROM 的配置

3.4、ROM IP 核的调用

(1)ROM 顶层模块代码

(2)ROM IP 核仿…

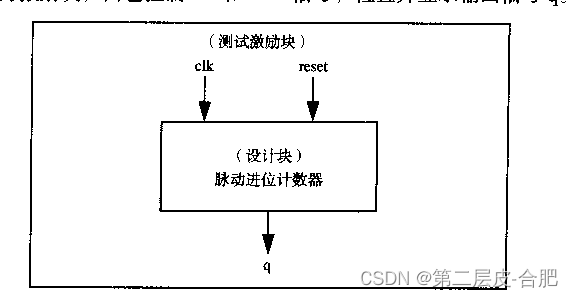

FPGA基础知识-层次建模的概念

学习目标:

提示:这里可以添加学习目标

理解数字电路设计中自底向上和自顶向下的设计方法;

解释verilog中模块和模块实例之间的区别;

学习从4中不同的抽象角度来描述同一个模块;

解释仿真中的各个组成部分…

[CS]通信科普相关博文分享

最近在学习通信相关基础知识,看到有相关不错的文章,分享下~~

无线通信TX的流程: L2 -> CRC -> turbo -> interleave -> scramble -> QPSK -> OFDM -> Preamble -> upsample -> RC filter -> upsample ->…

[HDLBits] Exams/m2014 q4g

Implement the following circuit: module top_module (input in1,input in2,input in3,output out);assign out (!(in1^in2))^in3;

endmodule

![[静态时序分析简明教程(十)]组合电路路径set_max/min_delay](https://img-blog.csdnimg.cn/8b22587582384a26958c97eb94073580.png)

![[FPGA IP系列] FPGA常用存储资源大全(RAM、ROM、CAM、SRAM、DRAM、FLASH)](/images/no-images.jpg)

![[FPGA IP系列] 2分钟了解FPGA中的BRAM](https://img-blog.csdnimg.cn/b4c99a625a2c4f84a061586a235d883d.png)

![[HDLBits] Exams/2012 q1g](https://hdlbits.01xz.net/mw/thumb.php?f=Exams_2012q1g.png&width=195)

![[HDLBits] Exams/m2014 q4g](https://img-blog.csdnimg.cn/img_convert/f63e666da5a7a7ce032c242a744414ea.png)